Projects >

Thermal Management of Microelectronic Devices

|

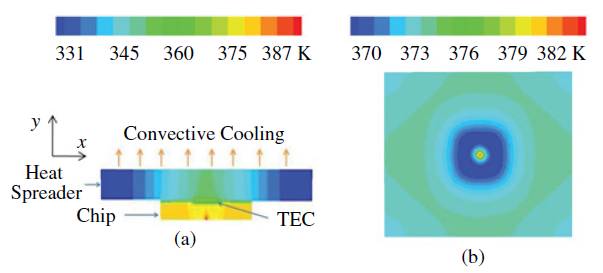

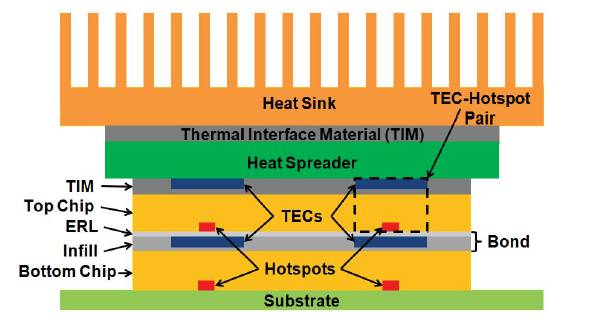

Mainstream Chip Package with single TEC

(a) Temperature contours in a vertical cross-section of an electronic package are shown [only heat spreader, TIM, chip, substrate, and TEC is considered for simulations. Convective heat transfer boundary condition is applied at the top of the spreader]. (b) Temperature contours on the bottom surface of the chip

. 3D stached chip packages with multiple TECs

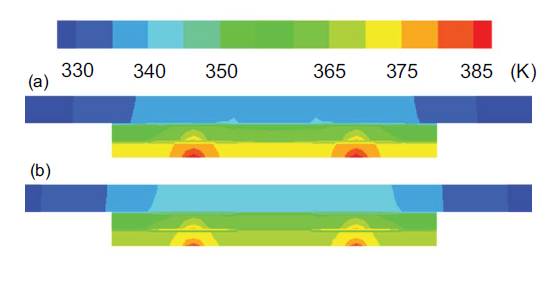

Temperature contour in a vertical cross section of electronic package. (a) Temperature contour with 0 A current through all four TECs. (b) Temperature contour with 1.75 A current through all four TECs. |

As microelectronic device size continues to be reduced, a physical limit will inevitably be reached. Current research efforts focus on new ways to improve the performance of microelectronic devices. One such avenue, 3-D stacked chips, involves stacking several active dies interconnected through silicon vias (TSVs). This novel architecture may reduce microelectronic form factor, improve performance by reducing interconnect delay, and provide a more energy-efficient chip design. However, these electrical and packaging benefits may be offset by the thermal concerns. Increased power density can become a daunting challenge for heat removal in the 3-D technology. Though it has been suggested that TSVs can be used for circuit-level thermal management, it is expected that widespread adoption of the 3-D technology will bring severe thermal management challenges at the package level. A severe thermal challenge in chips is the formation of hotspots, which occur on varying time and spatial scales. These hotspots, if not adequately cooled, result in high temperature gradients, which hurt chip performance and reliability. Modern chips generate average heat fluxes of around 100 W/cm2, but localized heat fluxes can be up to five times higher. Multiple efforts are underway to develop new methods of efficient cooling in 3-D electronics. These efforts include the use of microchannels, high-conductivity thermal interface materials, and solid-state thermoelectric coolers (TECs). Hybrid cooling systems including fluidic microchannels and TECs have also been investigated for hotspot cooling. Microchannels are suitable for high-performance applications where extreme heat fluxes are present. Since hotspots occur on varying temporal and spatial scales, cooling methods should be scalable on demand and actively controlled to cool hotspots as necessary. This is important to improve efficiency and reduce cooling costs. TECs are particularly suitable for on demand and activelycontrolled cooling at hotspots. TECs are solid-state devices whose operation is based on the Peltier effect. These devices output a temperature difference when a voltage is applied and can conversely output a voltage when a temperature difference is applied. In either function, they have the potential to play a role in sustainable technology innovations.. We investigate ultrathin thermoelectric coolers (TECs) for the energy efficient thermal management of hot spots. Our research analyzes the efficient usage of ultrathin TECs by focusing on important issues such as integration of these devices with electronic package, effect of parasitic contact resistances, utilization of appropriate current pulses and control algorithms. The study extends to analyzing coupled operation of multiple TECs in 2D and 3D stacked chips for cooling spatiotemporally varying hot spots in order to maintain the dynamic hot-spot temperature below a threshold. We are currently developing experimental set-up to investigate the operation of embedded TECs using on-chip resistance temperature detectors and thin-film based TECs.

|

|

Relevant Publications on Peltier Cooling 1. Matthew, R., Manickaraj, K., Sullivan, O., Mukhopadhyay, S. and Kumar, S., “Hotspot Cooling in Stacked Chips using Thermoelectric Coolers,” IEEE Transactions on Components and Packaging Technologies, 3 (5), 759-767, 2013. [PDF] 2. Sullivan, O., Alexandrov, B., Mukhopadhyay, S., and Kumar, S., “3D Compact Model of Packaged Thermoelectric Coolers,” ASME Journal of Electronic Packaging, 135, 031006, 2013. [PDF] 3. Sullivan, O., Gupta, M. P., Mukhopadhyay, S., and Kumar, S., “Array of Thermoelectric Coolers for On-Chip Thermal Management,” ASME Journal of Electronic Packaging, 134, 021005, 2012. [PDF] 4. Gupta, M., Sayer, M., Mukhopadhyay, S., Kumar, S., “Ultrathin Thermoelectric Devices for On-Chip Peltier Cooling,” IEEE Transactions on Components and Packaging Technologies, 21 (9), 1395-1405, 2011. [PDF]

Relevant Publications

on Power Mulitplexing: 1. Kersey, C., Gupta, M. P., Sathe, N., Kumar, S., Yalamanchili, S., and Mukhopadhyay, S., “Power Multiplexing for Thermal Field Management in Many Core Processors,” IEEE Transactions on Components and Packaging Technologies, 3 (1), 94-104, 2013. [PDF] 2. Gupta, M. P., Cho, M., Mukhopadhyay, S., and Kumar, S., “Thermal Investigation into Power Multiplexing for Homogeneous Many-Core Processors,” Journal of Heat Transfer, 134, 061401, 2012. [PDF]

Funding: NSF |

|